1 低位交织计算

CPU周期时间公式:

所需存储体(memory bank)的数量:

Example:

已知:CPU 时钟 = 200MHz,内存访问时间 = 50ns,求所需存储体数量和第 1 个 Bank 的地址。

Solution:

-

计算 CPU 周期:

-

计算存储体数量:

-

第 1 个 Bank 的地址:0,10,20,30…(步长 = 存储体数量)

2 两级内存层次平均访问时间计算

核心参数:

-

-

-

-

四个公式要背:

-

平均系统访问时间公式(The average system access time for a word):

展开公式得到:

-

块大小

-

访问效率公式:

Example:

主存访问时间

(a) Cache-主存层次:Cache 命中率

(b) 主存-硬盘层次:主存命中率

Solution:

(a)

速度提升:

结论:即使 H=0.7,也能大幅提升速度。

(b)

先进行单位转换:

因此,

块传输时间为:

所以,

则:

结论:即使

3 匹配逻辑布尔函数

- 单比特匹配逻辑:

(

-

带掩码的单比特逻辑:

-

单字完整匹配逻辑:所有位都匹配成功,该字才匹配成功,是所有位的逻辑与:

无掩码时(K 全 1),简化为:

最终可以化为: -

带元位(有效位)的匹配逻辑:

加入元位

有效匹配需要同时满足 “内容匹配

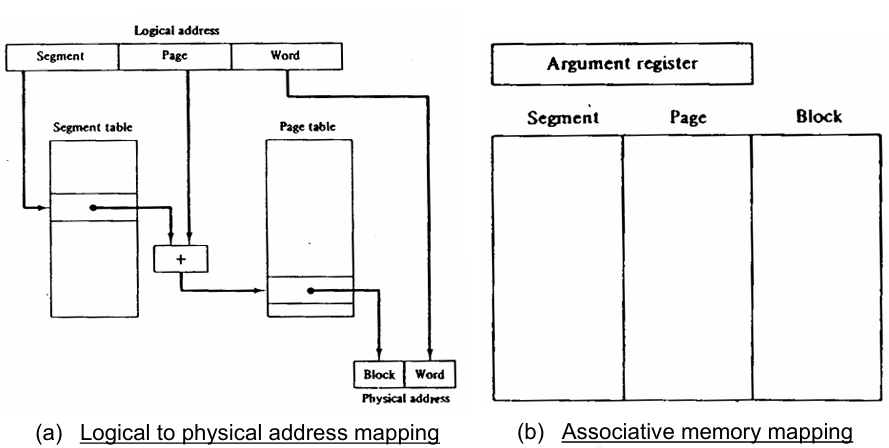

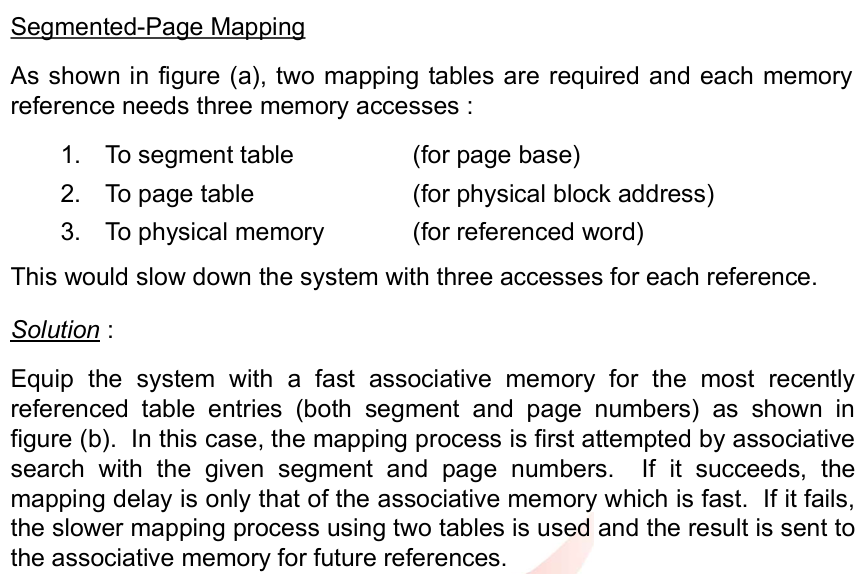

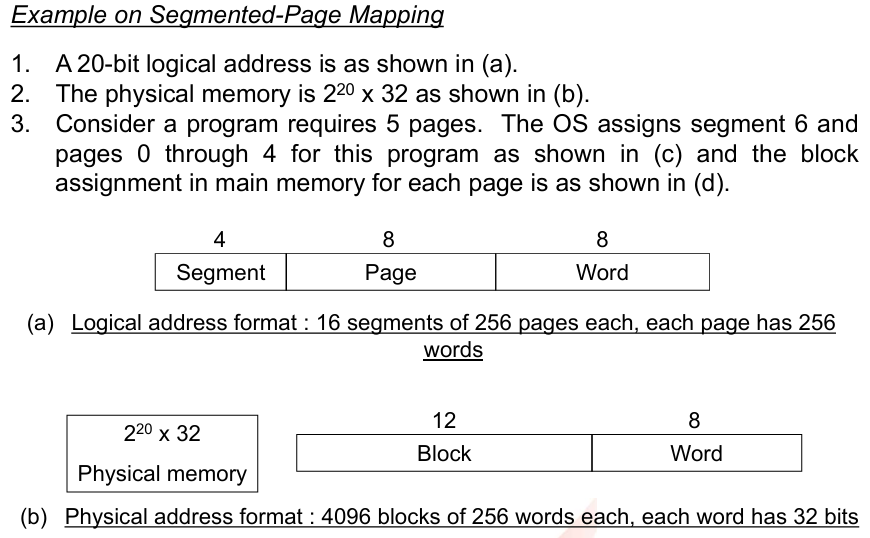

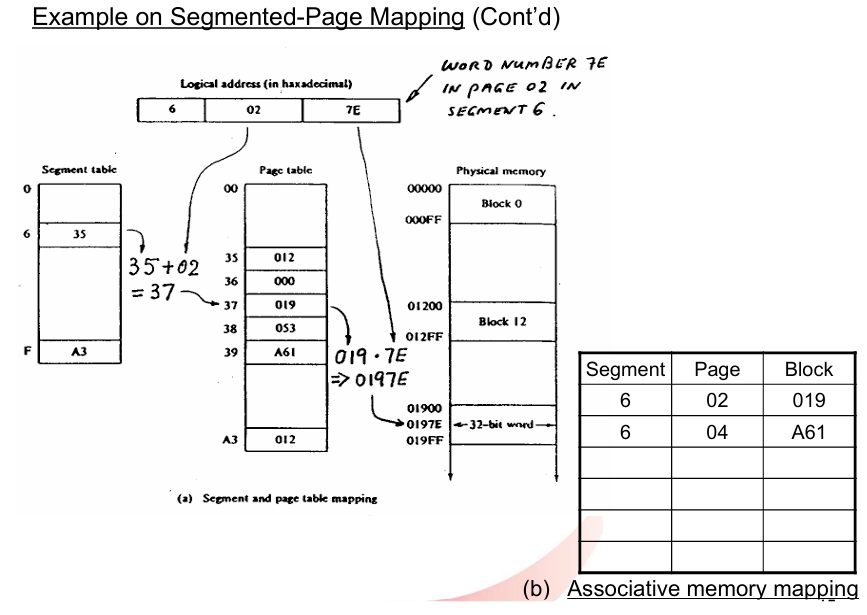

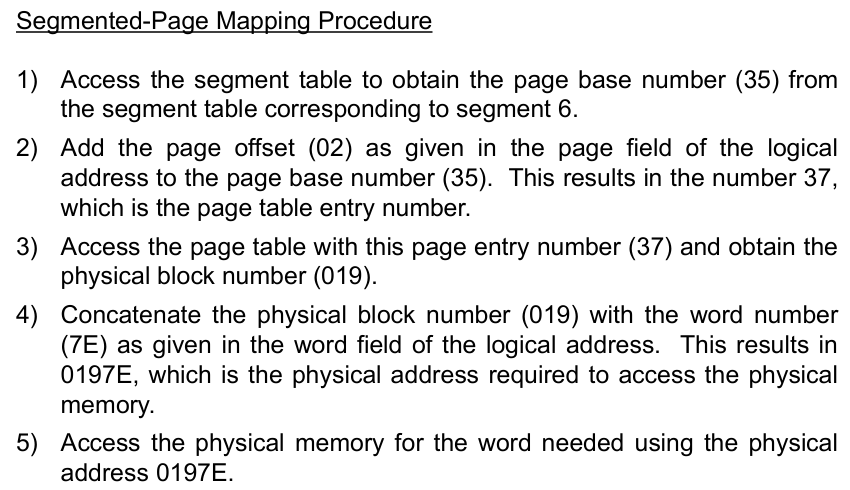

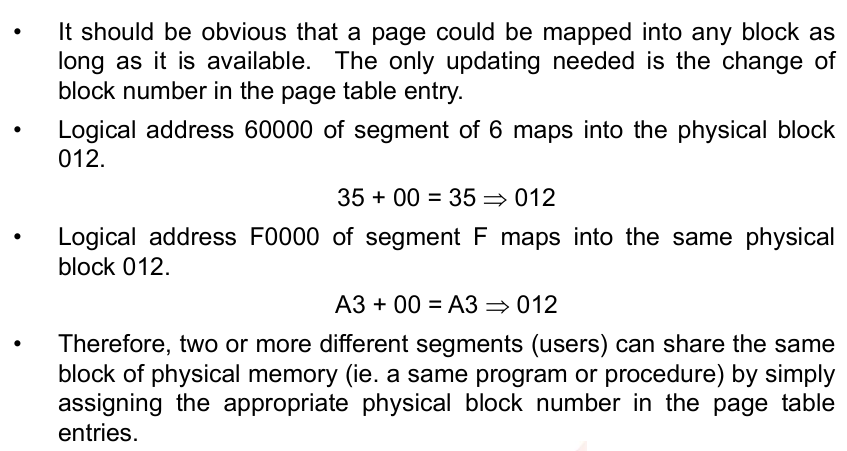

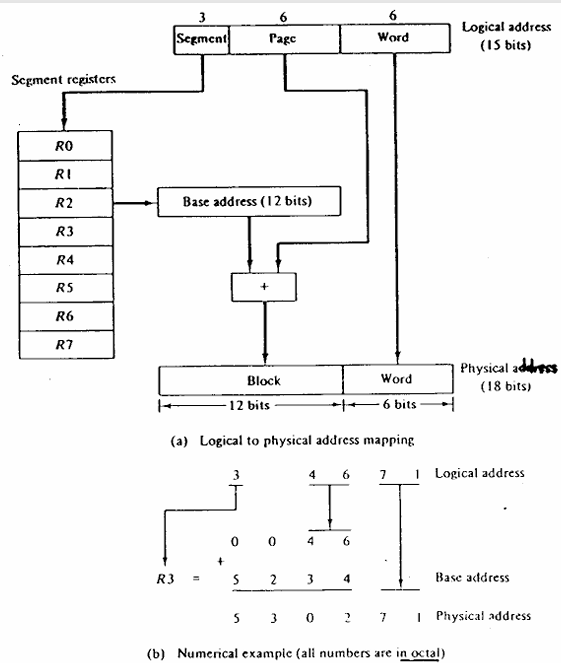

4 段页式映射(Segmented-Page Mapping))

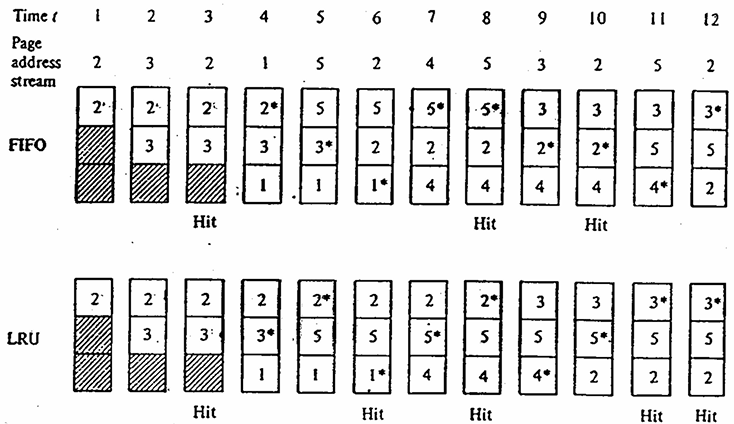

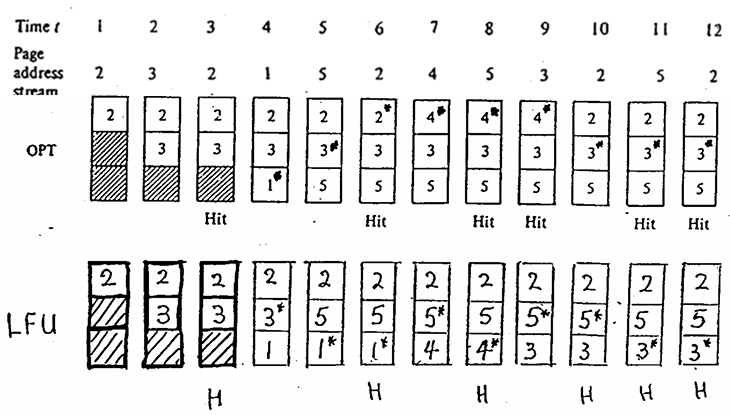

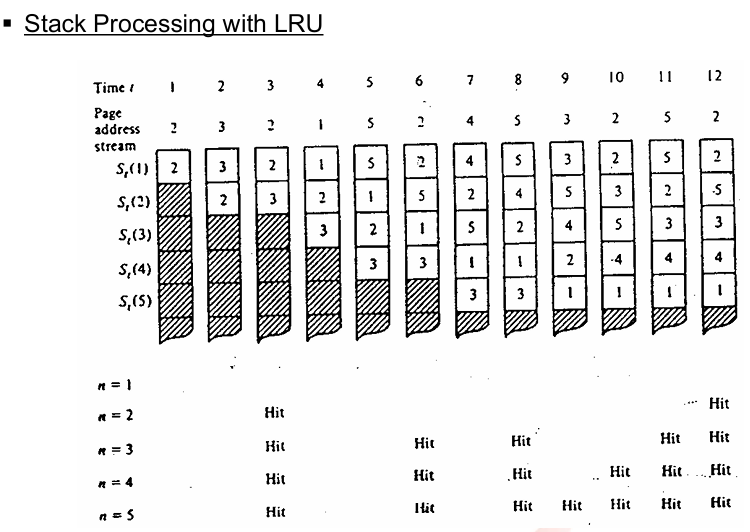

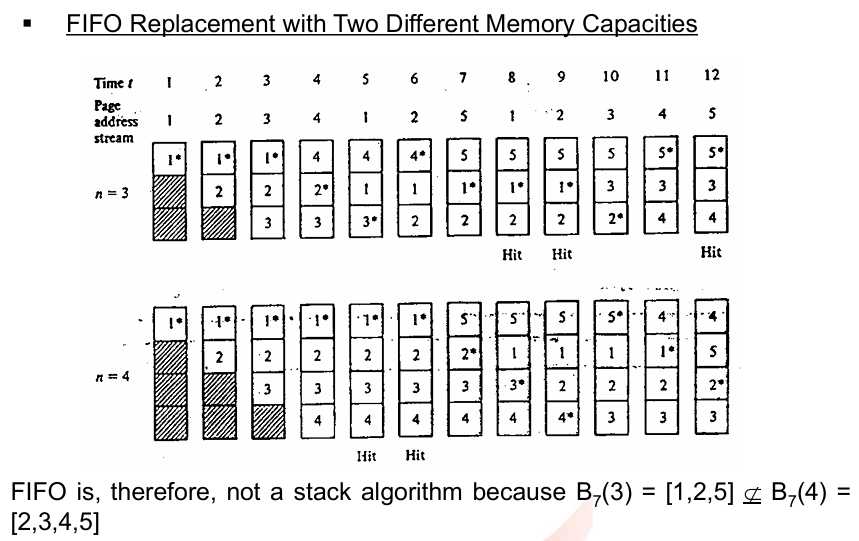

5 页面置换算法

Example:

Given a main memory size of 3 page frames for a given page stream of

2 3 2 1 5 2 4 5 3 2 5 2

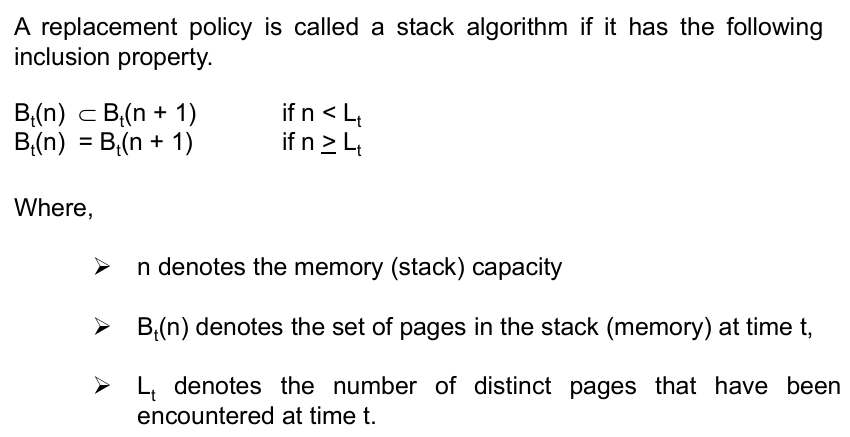

6 栈算法

7 页面大小优化与内存利用率

7.1 最优页大小计算

-

内存开销组成

-

内部碎片浪费:平均每个段的最后一页浪费

-

页表开销:页表有

-

总开销公式:

(

-

-

最优页大小推导

对

7.2 内存利用率 U 计算

核心公式:

代入最优页大小

- 当

- 当

- 核心结论:大型系统中,能获得最优命中率的页大小,通常远大于开销最小的最优页大小;系统性能优先时,优先保证高命中率,而非最小开销。

8 Cache 存储器

-

命中(Hit):CPU 要访问的字在 Cache 中

-

未命中(Miss):CPU 要访问的字不在 Cache 中

-

命中率(H):命中次数 / 总访问次数,命中率越接近 1,系统访问时间越接近 Cache 速度。

8.1 Cache-主存系统平均成本计算

核心公式:

其中,

-

-

-

-

Example:

If the cost of the cache memory is 10 times the cost of the main memory, and the total amount of memory required is 32 MB, determine the size of each type of memory to achieve a total memory cost of only 1.01 times the cost of the main memory.

Solution:

已知:

代入公式:

得:

约去

结论:仅增加 1% 的成本,就能大幅提升系统速度。

8.2 Cache性能计算

核心公式:

-

平均系统访问时间:

(

-

访问效率:

-

加速比:

加速比上限为

Example:

For a cache-main memory design, if

Solution:

已知:

- 代入公式:

- 化简得:

- 访问效率:

- 加速比:

9 性能度量指标

各项参数:

CPU 性能指标为 CPI:

每条指令周期数 (Cycles per instruction)

指令带宽 (

吞吐量(数据带宽

- MFLOPS 百万次浮点运算每秒:每秒百万次浮点运算

- GFLOPS 十亿次浮点运算每秒:每秒十亿次浮点运算

- 任务的执行时间 = 总时钟周期数 × 时钟周期时间

加速:

并行度:

效率:

9.1 并行计算机的性能分析(Amdahl 定律)

设 F 为所有浮点操作中以标量操作执行的比例, 那么 (1-F) 即为以向量操作执行的比例

设平均系统吞吐量为

有

然后再代入平均系统吞吐量的公式,

这里也可以看出,标量运算操作对系统平均吞吐量的影响。

加速比为

当

Example:

标量吞吐量

Solution:

Note that

If

当

当

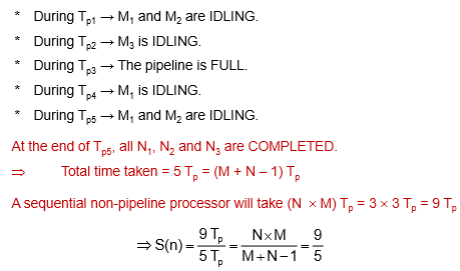

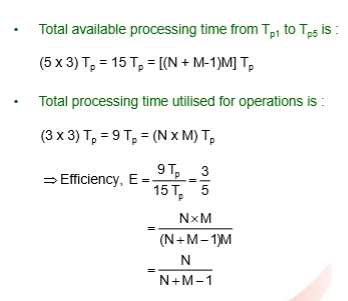

9.2 流水线的性能分析

假设每个阶段的处理周期时间为

从 Tp1 到 Tp5 的总可用处理时间为

[! note] 可以想象一个矩形,其长为完成

个任务所需要的时间;宽为流水线级数。

- 加速比就是使用流水线加速后,原本的完成时间与加速完成时间的比例;

- 流水线效率就是完成任务花费的时间(占用的面积)与总面积的比例。

Example:

已知M=3 级流水线,N=3 个操作,每个阶段时间均为

Solution:

- 串行总时间:

- 流水线总时间:

- 加速比:

- 效率:

- 吞吐量:

10 同步失败概率计算

核心公式:

-

进入亚稳态的概率

-

触发条件:触发器的输入信号在 孔径时间

-

孔径时间

-

计算公式:

其中:

-

-

等待后仍处于亚稳态的概率

-

原理:亚稳态的电压差随时间指数放大,等待时间越长,仍处于亚稳态的概率指数级下降。

-

计算公式:

其中:

-

-

同步失败频率

-

定义:单位时间内发生同步失败的次数,与异步信号的事件频率成正比。

-

计算公式:

其中:

-

-

平均无故障时间 MTBF

-

定义:两次同步失败之间的平均时间,是衡量同步器可靠性的核心指标。

-

计算公式:

-

Example:

Assume a Brute-force synchroniser with a 500MHz clock samples a 10MHz asynchronous input signal ,

The flip-flops have **aperture time(

What is the probability of synchronisation failure(

What is the frequency of synchronisation failure(

What is the mean time between synchronisation failures(

Solution:

-

统一单位:

-

计算进入亚稳态的概率:

-

计算等待后仍处于亚稳态的概率:

-

计算总失败概率:

-

计算失败频率:

-

计算 MTBF: